Hallo!

Lernen muss jeder selber: http://rn-wissen.de/wiki/index.php/O...erst%C3%A4rker .

Hallo,

ich habe da gerade folgendes auf dem Steckbrett aufgebaut:

Die Schaltung erkennt auch ganz gut die Lichthelligkeit, aberCode:VCC + | o---------. o--------------o | | | .-. | | |1| | | |M| | | '-' | | | | | o | |\| | | .------|+\ TLC272 o | | | >- ----------o ADC | '-----)------|-/ ---- | |/| ``/\ D1 | | -- | | | | | o----------------o--------o--------------o | === GND

ich habe da noch ein großes Problem, berühre ich das Steckbrett,

geht der TLC fast auf High.

Was mache ich hier falsch?

Die Schaltung habe ich aus einem Schaltplan abgekupfert. Allerdings gib es

da noch eine Leitung von OUT über einen 10K nach VIN-.

Habe ich das Richtig verstanden, dass der TLC dann als Differenzverstärker arbeitet?

Das was ich benötige ist allerdings eine Lineare Verstärkung, da ich nur am ATMEGA

messen möchte wie hell es gerade ist.

PS: Den TLC Verwende ich da dieser schon erfolgreich mit der A-Seite Tonerkennung

durchführt, da verstehe ich dass er als Differenzverstärker arbeiten soll, da ja der unterschied

verstärkt werden soll.

Hallo!

Lernen muss jeder selber: http://rn-wissen.de/wiki/index.php/O...erst%C3%A4rker .

MfG (Mit feinem Grübeln) Wir unterstützen dich bei deinen Projekten, aber wir entwickeln sie nicht für dich. (radbruch) "Irgendwas" geht "irgendwie" immer...(Rabenauge) Machs - und berichte.(oberallgeier) Man weißt wie, aber nie warum. Gut zu wissen, was man nicht weiß. Zuerst messen, danach fragen. Was heute geht, wurde gestern gebastelt. http://www.youtube.com/watch?v=qOAnVO3y2u8 Danke!

Hallo,

erst mal danke für den Link.

Aber je mehr ich lese desto verwirrter bin ich. Ich experimentiere hier gerade mit dem Licht- und einem Audio Sensor.

Liege ich damit richitg, dass die oben gezeichnete Schaltung so sensibel ist, da ich keinen Rückfluss von Out auf VIN- über

einen Widerstand habe und somit der OAMP nicht begrenzt ist? Und er wirklich unendlich verstärkt?

Hier noch ein zweiter Fall, der zwar funktioniert aber sich mich überhaupt nicht erschliesst.

Kann mir jemand diese Schaltung evtl. erklären? .... Ich hatte leider kein E Technik als Software Entwickler

Ich hoffe dass ich schon mal folgendes richtig verstanden habe.Code:.-------------------------------- | VCC | .-. 22k 22k| | ___ | | o-|___|-o '-' | | | | | o | |\ | | 100nF .---o-|-\ | _ | || | | >--o--------o | / \--o---o-||-o---)---o-|+/ ADC |(Mic) || | |/ TLC272 | \_/--o | | --- | === 4,7µ | | '-------------------------------- GND

- Das MIC wird über den 22k und GND versorgt und erzeugt dabei eine Schwingung bei Schall, die aufmoduliert wird.

- Diese wandert über den 100nF wobei der Gleichstromanteil eliminiert wird.

- Jetzt kommt die Schwingung beim TLC an, dieser verstärkt jetzt das Signal und gibt es auf OUT1 aus.

- Von dort erfolgt eine Rückkopplung zu VIN- über den 22k Damit wird auch die Verstärkerleistung begrenzt?

--> Das Austauschen dieses Widerstands bringt ein anderes Klangbild (mit Kopfhöherer getestet) also vermute ich dass das Ganze noch irgendwie als Filter wirkt?

- Des weiteren habe ich bemerkt dass die Verstärkung dabei nie einen Maxpegel von 5V erreicht. (Dachte immer der 22k bei der Rückkopplung wäre die Grenze???)

Kann hier jemand Licht ins Dunkel bringen?

Ich würde gerne verstehen wie das Funktioniert. Aber inzwischen verstehe vor

Verstärker, Invertierter Verstärker, Differenzialverstärker und den Schaltbildern, die sich nur wenig ändern langsam gar nichts mehr.

. . . Der Knoten im Kopf wird mit jedem Datenblatt und jeder Erklärung irgendwie grösser.

So dass ich auf eure Hilfe angewiesen bin.

Manchmal frage ich mich, wieso meine Generation Geräte ohne Simulation entwickeln konnte?

@ Tux12Fun

Du hast alles richtig verstanden, deshalb habe ich nur kurz deine Fragen mit "?" beantwortet. Sollte noch etwas unklar sein, bitte weiter Fragen !

Theoretisch ja, aber praktisch hat ein OPV ohne negativer Rückkopplung (von Out auf VIN-) nur endliche sehr große Verstärkung (zig Tausend). Deine Schaltung verhält sich deshalb als Komparator und schaltet gegen 0 V zwischen GND und fast VCC um.

Ja und die Verstärkung des OPVs in dieser Schaltung ist fur bestimmte Frequenz (F) gleich Widerstand (R) 22k geteilt durch Scheinwiderstand (XC) des Kondensators (C) 4,7 µF, also Ku = R / XC, wobei XC = 1 / 2 * pi * F * C .

Ja. Weil XC mit wachsender Frequenz sinkt, bildet die Schaltung einen Hochpass (Filter).

Bei realem OPV erreicht die Ausgagsspannung praktisch nie volle VCC. Für TLC272 bei VCC = 5 V erreicht die Ausgangsspannung VICR max. ca. 3,5 V. Das sieht man im Datenblatt (DB) auf 5. Seite: http://www.datasheetcatalog.com/data...2/TLC272.shtml.

Sonst habe ich für dich noch ein Hinweis: bitte zukünftig auf Schaltplänen jedes Bauteil eindeutig beschriften (Widerstände mit RX, Kondensatoren mit CX, usw., wobei X ist laufende Nummer). Das verkleinert eben enorm die Diskussion über eine Schaltung.

MfG (Mit feinem Grübeln) Wir unterstützen dich bei deinen Projekten, aber wir entwickeln sie nicht für dich. (radbruch) "Irgendwas" geht "irgendwie" immer...(Rabenauge) Machs - und berichte.(oberallgeier) Man weißt wie, aber nie warum. Gut zu wissen, was man nicht weiß. Zuerst messen, danach fragen. Was heute geht, wurde gestern gebastelt. http://www.youtube.com/watch?v=qOAnVO3y2u8 Danke!

Hallo,

jetzt muss ich den Beitrag nochmal erweitern.

Also der Grundschaltungsteil mit Tonerkennung läuft jetzt gut, aber nur solange ich nicht für mein Display die PWM für die Helligkeitsreglung aktiviereab dem Zeitpunkt habe ich dann ein Pfeifen am TLC Ausgang.

Ich nehme mal an, dass man da nicht all zu viel machen kann, da die PWM ja ein Signal moduliert, dass dann am Steckbrett schon von den Drähten gesendet wird.

Die PWM ist wie folgt aufgebaut:

OC1A ------ FET ------- Display ------- GND

Vielleicht hat ja jemand doch einen Tipp für mich.

Denke mal Masseflächen auf der späteren Platine sollte ich auf jeden Fall einplanen oder?

Algemein könnte ich nur sagen, dass man die für mich undefinierte PWM Sache bzw. die Antennen (Drähte) gut abschirmen muß oder die Helligkeitspannung vor dem Zuführen zum Display mit RC Tiefpaß also seriellem Widerstand und genug großem Kondensator am GND glätten.Code:R ___ PWM >---|___|-+---> zum Display | --- --- C | === GND (created by AACircuit v1.28.6 beta 04/19/05 www.tech-chat.de)

MfG (Mit feinem Grübeln) Wir unterstützen dich bei deinen Projekten, aber wir entwickeln sie nicht für dich. (radbruch) "Irgendwas" geht "irgendwie" immer...(Rabenauge) Machs - und berichte.(oberallgeier) Man weißt wie, aber nie warum. Gut zu wissen, was man nicht weiß. Zuerst messen, danach fragen. Was heute geht, wurde gestern gebastelt. http://www.youtube.com/watch?v=qOAnVO3y2u8 Danke!

Danke für deine Antwort.

Sollte das R C Glied dann nach dem FET (IRLML6402TR) sitzen?

Da mein FET direkt mit 5V umgehen kann hatte ich gar kein R dazwischen.

Nehme ich die Last vom FET (Display abstecken) habe ich nur noch ein leichtes Pfeifen, dass ich über den TLC höre.

Der ATMEGA läuft mit 16 MHZ und die PWM ist im Moment wie folgt definiert.

Das schnipsel stammt aus dem WEB.Code:DDRD |= _BV(PD5); TCCR1A = (1<<WGM11) | (1<<WGM10) | (1<<COM1A1); // 10bit-Counter, nicht invert. PWM TCCR1B = (1<<CS10); // Pre-Scaler = 1, also ohne Teiler OCR1A = 500;

Den OCR1A = Wert ändere ich für die Helligkeit des Displays.

Der Pfeifton beginnt sobald die PWM aktiv wird und geht dann fast über den ganzen Bereich, habe das mit OCR1A = i in einer Schleife von 0 - 1023 getestet

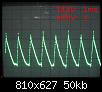

Und so sieht das am OSZI aus, wenn ich GND und OUT vom TLC messe.

Geändert von Tux12Fun (02.06.2015 um 00:53 Uhr)

Ja, damit in der Leitung zum Display praktisch keine PWM mehr gibt.

Sorry, aber chinesisch verstehe ich leider nicht.

Möglicherweise könnte das Trennen von analoger (AGND) und digitaler (DGND) Masse nötig sein. Die beiden dürfen nur in einem Punkt am Versorgungspol verbunden werden, damit in AGND kein Strom I2 fließt.

Aus gleichem Grund könnte eine Trennung der Versorgung (VCC) auf analoge (UA) und digitale (U) Versorgungsspannung per Tiefpaß (R, CA1, CA2) notwendig sein.Code:+-----------+ +-----------+ | /------\ | | /------\ | .-.| | | | | |.-. RL1| || | /+\ /+\ | || |RL2 | || |( U1) (U2 )| || | '-'| I1 | \-/ \-/ | I2 |'-' | \-->---/ | | \---<--/ | +-----------+--------+--------+-----------+ AGND | DGND === GND (created by AACircuit v1.28.6 beta 04/19/05 www.tech-chat.de)Ohne detailiertem Schaltplan kann ich darüber nix mehr sagen.Code:VCC R + ___ | +----------+------+---+-|___|-+---+------+------------+ | /------\ A | | | | | /------\ | .-.| | | | |+ | |+ | | |.-. RL1| || | |UA --- === --- === /+\ | || |RL2 | || | | --- /-\ --- /-\ ( U ) | || | '-'| I1 | | CA1| |CA2 C1| |C2 \-/ | I2 |'-' | \-->---/ | | | | | | \---<--/ | +----------+------+---+-------+---+------+------------+ AGND | DGND === GND (created by AACircuit v1.28.6 beta 04/19/05 www.tech-chat.de)

Geändert von PICture (02.06.2015 um 07:39 Uhr)

MfG (Mit feinem Grübeln) Wir unterstützen dich bei deinen Projekten, aber wir entwickeln sie nicht für dich. (radbruch) "Irgendwas" geht "irgendwie" immer...(Rabenauge) Machs - und berichte.(oberallgeier) Man weißt wie, aber nie warum. Gut zu wissen, was man nicht weiß. Zuerst messen, danach fragen. Was heute geht, wurde gestern gebastelt. http://www.youtube.com/watch?v=qOAnVO3y2u8 Danke!

Hallo,

Dein Problem liegt im Aufbau, nicht in der Software.

Mach mal ein Foto, vielleicht sieht man die Möglichkeiten für ein paar Verbesserungen!

z.B. je nachdem wo so ein Draht an Masse angesteckt wird, wird dein Problem grösser oder kleiner

Was nimmst du als Stromversorgung? So ein 9V-Block, kann leicht in die knie gehen. Dann hast du das PWM-Signal überall auf der Versorgungsspannung!

Diese Steckbrettaufbauten sind für etwas anspruchsvollere Aufgaben, eigentlich ungeeignet.

Da sucht man dann gerne tagelang nach Fehlern und die Ursache sind dann Übersprechen im Aufbau oder eine schlechte Übergangswiderstand bei einer Steckung.

Vor der Erfindung der Leiterplatte hatte man Hartpapierstreifen mit aufgenieteten Lötösen, damit wurden auch Seriengeräte aufgebaut. Wer mal ein altes Röhrenradio gesehen hat, kennt die. Dieser Aufbau hatte sich bis in die 70er Jahre auch im Profibereich für Prototypen teilweise erhalten. Später auch begleitet von Vero-Board und Stechbrettern, wie heute noch. Damals wurde aber auch bei den Profis noch viel nach Trial ans Error entwickelt.

Ein Problem war, wie oben schon geschrieben, dass man oft Fehler gesucht, hatte, welche vom Aufbau kamen. Bei der Umsetzung in eine Leiterplatte, kamen dann neue Fehler dazu

Mit dem Aufkommen der µC waren dann diese Art von Aufbauten sowieso zu mühsam. CPU, RAM, ROM, Parallel Port, Timer. UART usw. waren noch alles einzelne ICs. Da dauerte schon das verdrahten des Datenbusses eine Ewigkeit

Es war dann einfacher zuerst die Schaltung und eine Leiterplatte zu entwerfen.

MfG Peter(TOO)

Manchmal frage ich mich, wieso meine Generation Geräte ohne Simulation entwickeln konnte?

Lesezeichen